## Automated PCB Parasitics Extraction from EDA Tools for Power Electronics Design Support

Sven FIEßER, PhD student, Technical University Ilmenau

## **Personal Introduction**

#### Sven Fießer

**PhD Student:** Research in HV-SMPS for magnetron applications and SMPS/PCB design at the Technical University Ilmenau

In cooperation with: University of Applied Sciences Fulda, Germany

#### Prof. Dr.-Ing. Ulf Schwalbe

University of Applied Sciences Fulda

- Renewable Energies

- E-Mobility

- Power Electronics

- Energy Storage

Systems for Grid

Integration

# Agenda

- 1. Background Information

- 2. Methods for Parasitic Extraction

- a. Inductances and Resistances

- b. Capacitances

- 3. Verification

- 4. Automated Parasitic Extraction

- 5. Simplification by Critical Path Extraction

- 6. Conclusion

## **Background Information**

Parasitic components in every power converter

Results in unwanted ringing in the switching elements

Increasing the power density by higher switching frequencies (e. g. with GaN and SiC semiconductors)  $\rightarrow$  Low parasitic PCB components are necessary

$\rightarrow$  Several design iterations until a good layout is created

$\rightarrow$  Reduce design process by evaluating its effects while routing the PCB

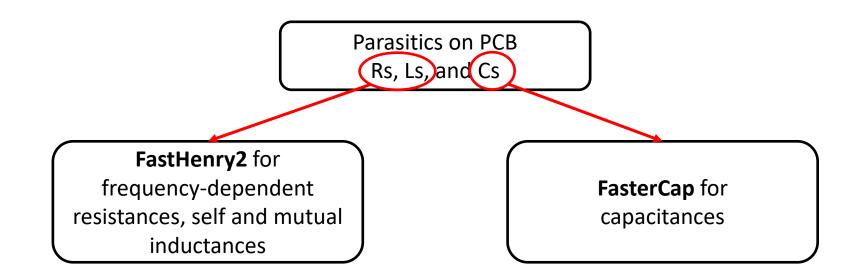

## **FastHenry**

- Developed at M.I.T. on Unix platform

- For the solution of Maxwell equations and extraction of inductances and resistances (includes coupling effects) in 3D

- FastHenry2 as a Windows porting

## **FastCap**

- Developed at M.I.T. on Unix platform

- For the solution of Maxwell equations and extraction of capacitances in 3D

- FastCap2 as a Windows porting

- FasterCap with several improvements (lossy dielectrics, automatic mesh refinement, ...)

Source: fastfieldsolvers.com

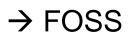

#### **FastModel**

Windows 3D viewer and text editor for FastCap2, FasterCap and FastHerny2

Download:

<u>www.fastfieldsolvers.com/download.htm</u> (contact form can be left empty)

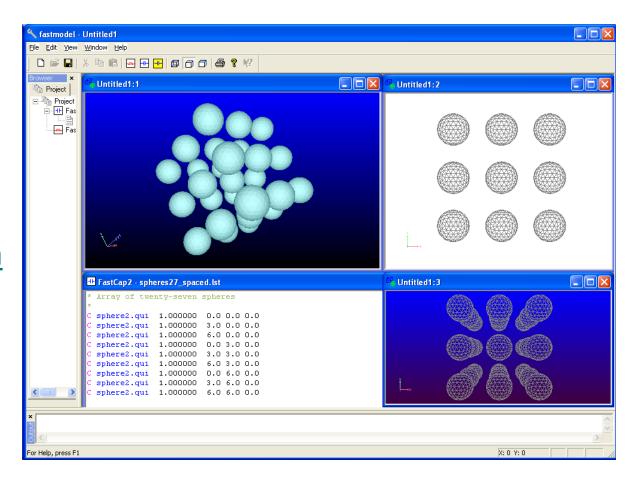

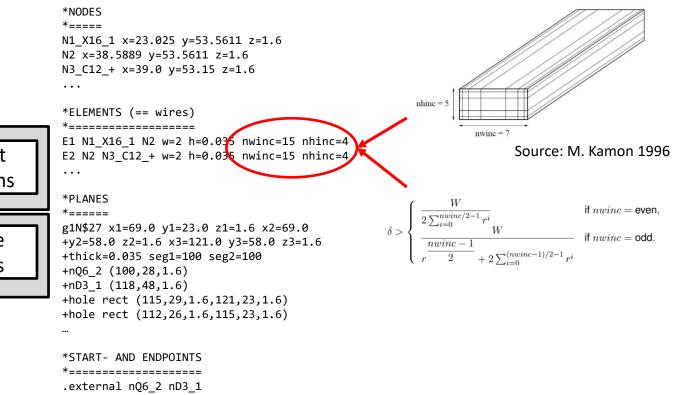

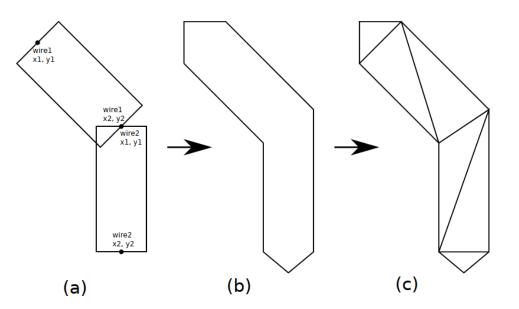

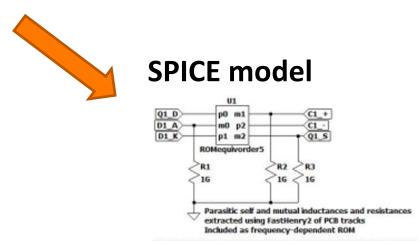

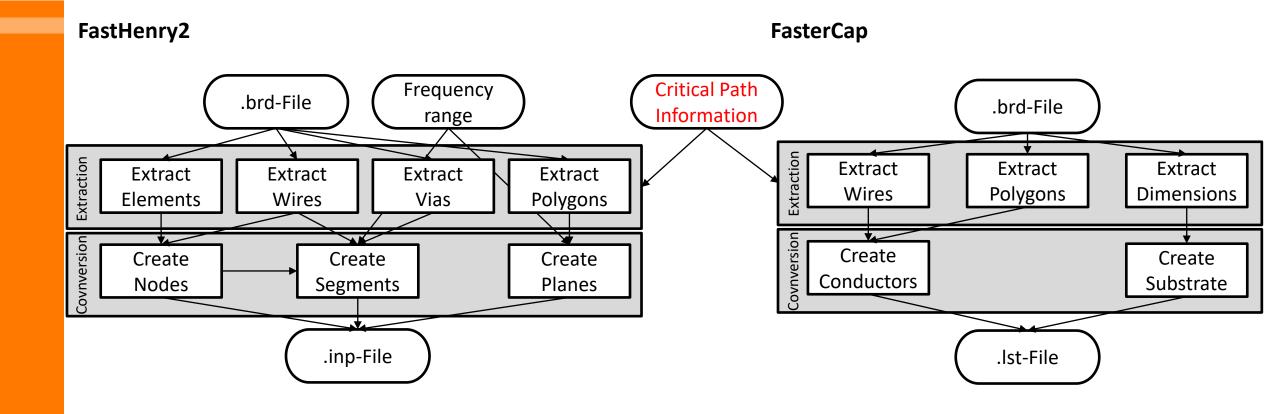

## **Converter for FastHenry2**

## <u>Input</u>

- Geometry of the copper traces in 3D using

- Elements (connection between two Nodes)  $\rightarrow$  Wires

- Planes (incl. Holes)  $\rightarrow$  Planes

- Frequency range

- Material properties of the copper (conductivity)

## <u>Output</u>

- Maxwell matrix for each frequency

- SPICE model

#### **Converter for FastHenry2**

.Units MM .Default z=0 sigma=5.8e4

\*FREQUENCY RANGE

. . .

\*============ .freq fmin=100 fmax=100e6 ndec=1 .end

## **Converter for FasterCap**

<u>Input</u>

- Geometry of the copper traces and PCB in 3D using

- Triangles or Squares

- Material properties of the PCB (relative permittivity)

$\rightarrow$  for FR4 approx. 4 (see datasheet)

<u>Output</u>

• Maxwell matrix

#### **Converter for FasterCap**

- For FasterCap only a rough mesh is needed → FasterCap does the mesh refinement (FastCap needs this to be done by hand)

- The meshing is done using **Gmsh** www.gmsh.info

#### **Example FastHenry2 - Backend**

Omicron Lab Symposium 2022 Sven Fießer Page 12

Hochschule Fulda

University of Applied Sciences

**ILMENAU** UNIVERSITY OF

TECHNOLOGY

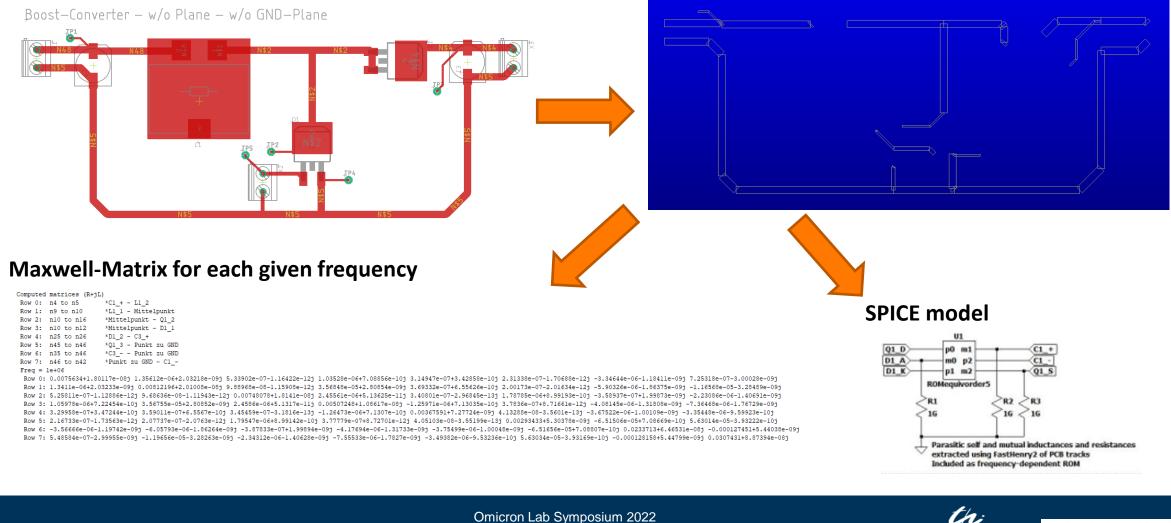

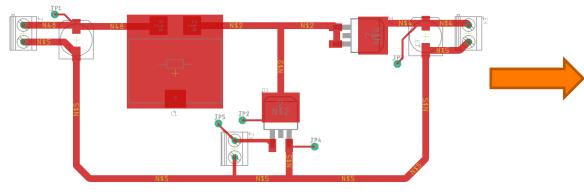

#### **Example FastHenry2 - Frontend**

Boost–Converter – w/o Plane – w/o GND–Plane

|   | Name  | L     | R    | ΔL     | ΔR     |

|---|-------|-------|------|--------|--------|

| • | Cond1 | 10 nH | 1 mΩ | - 10 % | - 11 % |

|   | Cond2 | 15 nH | 2 mΩ | + 15 % | + 16%  |

|   | Cond3 | 20 nH | 3 mΩ | - 10 % | - 11 % |

|   |       |       |      |        |        |

#### Extraction process for FasterCap is similar

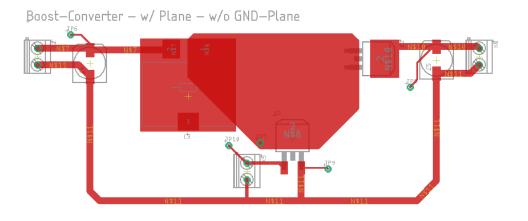

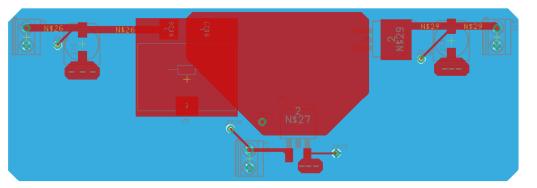

#### **Optimization Process**

#### **Exemplary optimization by**

1. Insertion of a plane in the critical path

Boost-Converter - w/ Plane - w/ GND-Plane

2. Insertion of a ground plane

$\rightarrow$  Evaluation of the parasitic components and its influences

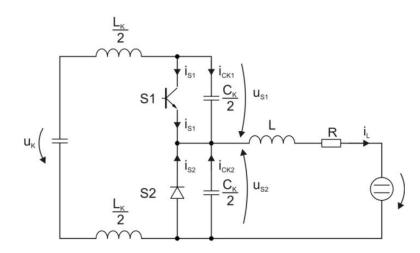

## Verification

- 1. Autodesk EAGLE

- 2. RCL extraction from EAGLE

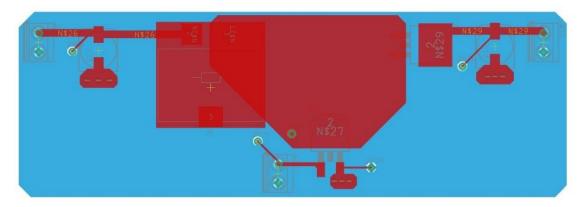

#### Boostconverter in EAGLE:

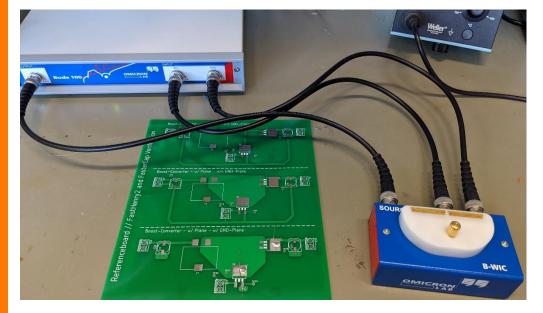

# 3. Boostconverter-PCB verification setup

#### Boostconverter-PCB for verification:

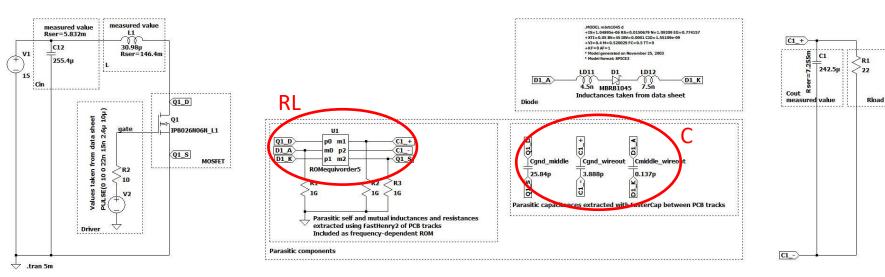

# Verification

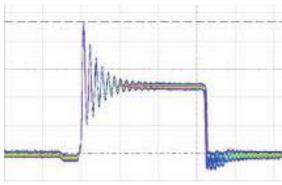

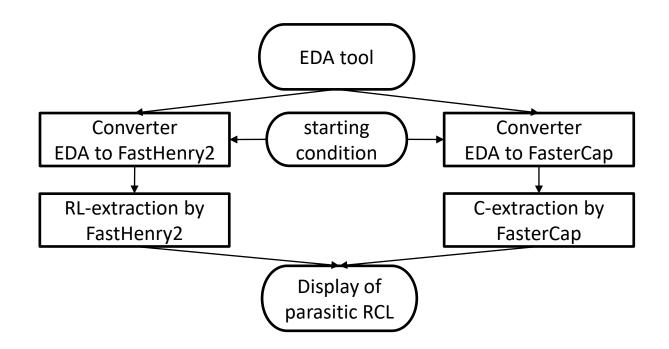

- 4. SPICE simulation

- a. Parasitic RCL included

- b. Switch/Diode models included

- 5. Comparison simulation and actual board

# $\begin{array}{c} 30 \\ - \\ 20 \\ 20 \\ 20 \\ 10 \\ 0 \\ 0.0 \\ 0.5 \\ 1.0 \\ 1.5 \\ 2.0 \\ 2.5 \\ 3.0 \\ 2.5 \\ 3.0 \\ 2.5 \\ 3.0 \\ 2.5 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3.0 \\ 3$

[s]

#### Comparison simulated and measured data:

#### SPICE simulation including PCB parasitics:

Omicron Lab Symposium 2022 Sven Fießer Page 16

1e-6

## Verification

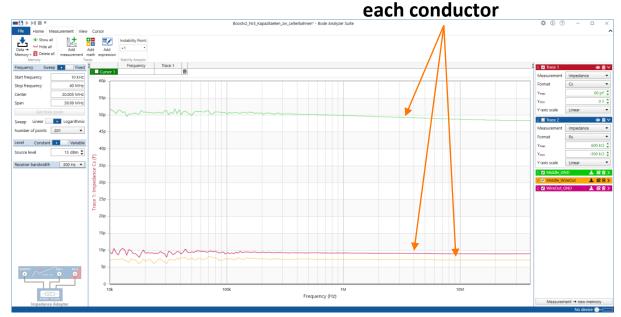

#### Measurement of the parasitic capacitances between the wires using the Bode 100 from Omicron Lab.

$\rightarrow$  Measured capacitances match quite the simulated values.

## **Benefits**

- Why go through so much trouble?

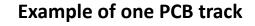

- Why not use the rule of thumb for inductance of PCB tracks? → 8 nH/cm

- Pro: Con:

- + easy

Width and height neglected

No skin effect (f<sub>ringing</sub> > f<sub>s</sub>)

No coupling effects (e. g. GND-planes)

- → Proper selection of switching components (V<sub>ds\_max</sub> and P<sub>v\_max</sub>)

- $\rightarrow$  Proper dimensioning of snubber elements

Source: www.powersystemsdesign.com/articles/pcb-layout/22/5871

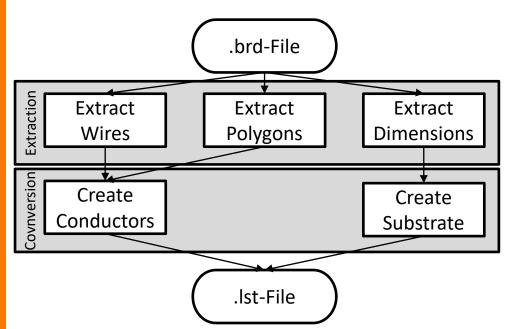

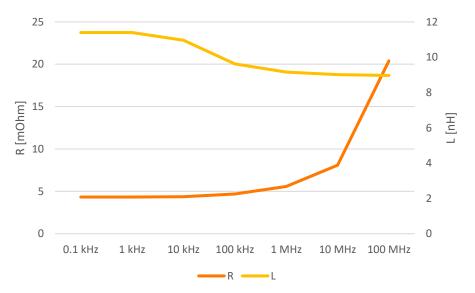

## **Automated Parasitic Extraction**

Second program for continuous RCL extraction

Omicron Lab Symposium 2022 Sven Fießer *Page* 19 ILMENAU UNIVERSITY OF H TECHNOLOGY

<u>Problem</u> so far: The converters convert <u>every</u> wire on the PCB <u>Solution</u>: Tell the converters which wires to extract

$\rightarrow$  only in the critical path

Not everyone knows where the critical path in every converter is  $\rightarrow$  Calculate it

## **Extraction using SPICE**

- 1) Creation of a (ideal) SPICE file.

- 2) Run the simulation and parse the waveform file.

- 3) Calculate *di/dt* and *du/dt* of every waveform according to equation 1.

- 4) Calculate the rms value of the differentiated waveforms according to equation 2. The highest values indicate the critical path.

$$\frac{\Delta x}{\Delta t} = x_{t+1} - x_t \tag{1}$$

$$RMS \ of \ diff. \ waveform = \sqrt{\frac{\sum_{i=1}^{n} (\frac{\Delta x_i}{\Delta t_i})^2}{n}} \tag{2}$$

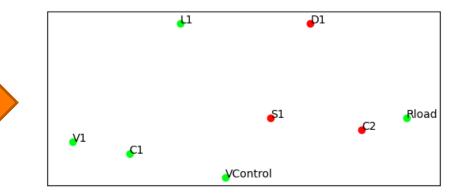

Ideal boost converter used for the critical path extraction

Graphical output of each element from the Simulation color-coded (red: critical path)

Omicron Lab Symposium 2022 Sven Fießer Page 23 ILMENAU UNIVERSITY OF H

## **Current and Future Works and Limitations**

- Parasitic extraction works well with "easy" geometries

- Wires and planes on top of each other not supported yet

- How to prevent GIGO:

- PCB must be modelled correctly

- Correct SPICE models of switching elements

- ESR/ESL of capacitances must be modelled correctly (→ e. g. with the Bode 100)

- Publication of the tool as soon as every bug is fixed

## Conclusion

The critical path in any given power converter can be found. The parasitic components can be simulated before the PCB is manufactured.

Especially in the high-frequency switching domain this evaluation comes in handy to shorten the PCB design process by reducing the design and testing iterations.

## Contact

#### M.Sc. Sven Fießer

Technical University Ilmenau Ehrenbergstraße 11 98693 Ilmenau, Germany sven.fiesser@tu-ilmenau.de

### Prof. Dr.-Ing. Ulf Schwalbe University of Applied Sciences Fulda Building 33, Room 113 Leipziger Straße 123 36037 Fulda, Germany ulf.schwalbe@et.hs-fulda.de