# Power Supply Compensator Design Using Operational Transconductance Amplifiers

Expert from Biricha Digital's Power Supply Design Workshop

Register here for free resources and future workshops www.biricha.com/omicron.html

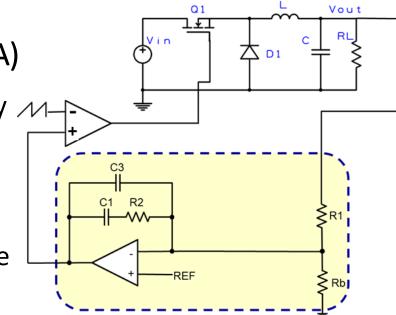

#### Peak Current Mode Control Compensator Design (with an OTA)

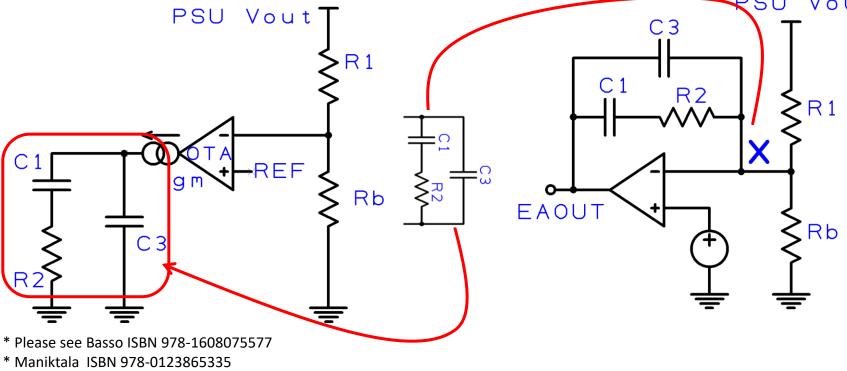

- As you may already be aware, for current mode control we usually only need a Type II compensator as shown on the right

- Type II design with a *standard op-amp* is well documented\*

- However, sometimes PWM ICs contain an internal "Operational Transconductance Amplifier" (OTA) instead of the standard voltage amplifier

- Advantages  $\rightarrow$  usually cheaper

- Disadvantage:

BIRICHA DIGITAL

- Can't easily make a Type III with an OTA

- Isolated loop design process is not well defined or documented

- For completeness we will design our next converter using a transconductance amplifier

- We will use the extremely popular LM515x range of controllers to show an example of compensator design using OTAs

Before we start our design, let us review Transconductance Amps

\* Please see Basso ISBN 978-0071823463 \* Maniktala ISBN 978-0123865335 Imode: 4 - 3 © S. A. Shirsavar - Biricha Digital Power Ltd 2024

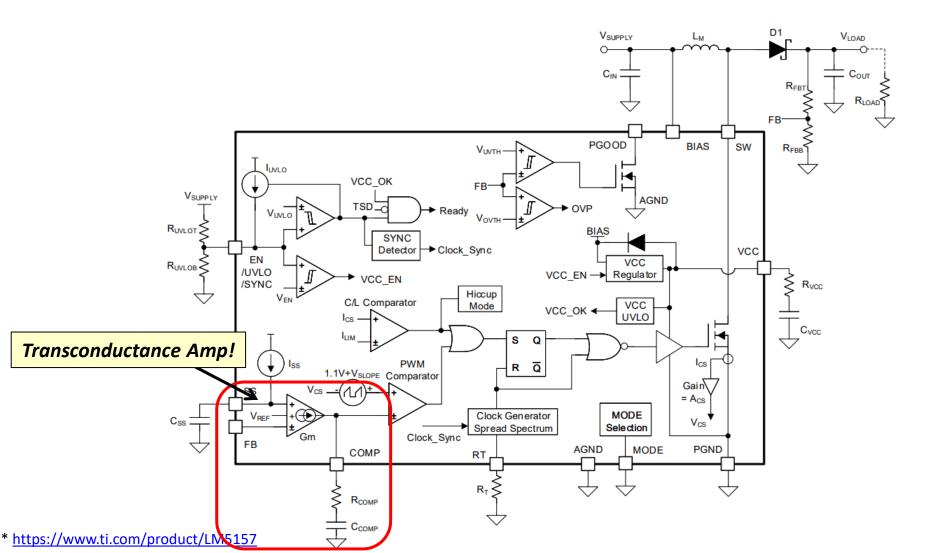

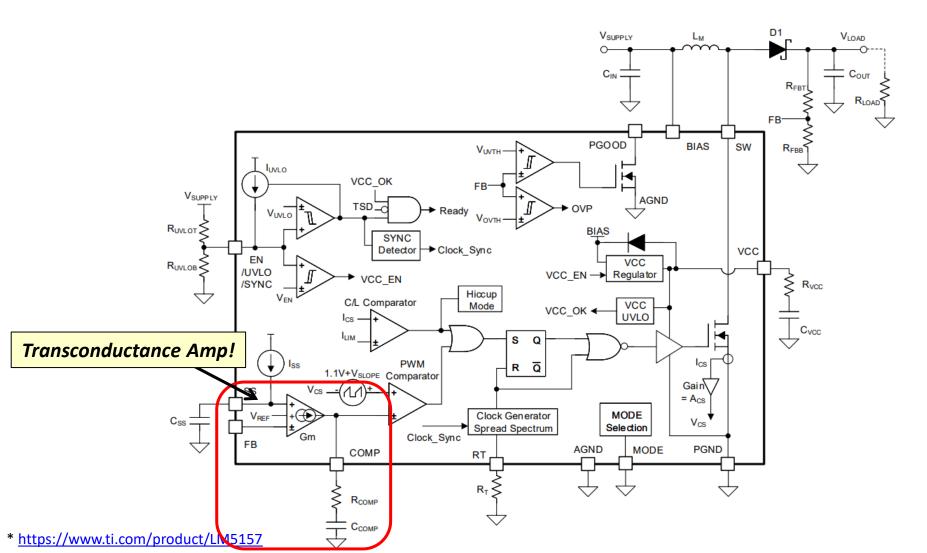

- We will use a TI LM5157\*:

- Internal switch

- Internal slope

- Ramp size in datasheet

- Internal current sense circuitry including signal amplification

- Current Sense Gain from datasheet

- A Transconductance Amplifier

- VREF and Gm in datasheet

#### Voltage Sources, Current Sources and Transconductance Amplifiers

Some of the very first topics that we study in electronic engineering are ideal voltages sources and op-amps

- Typically only Voltage Operational Amplifiers i.e. standard op-amps

- Typically voltages sources are covered in depth but current sources are usually only mentioned briefly

- Operational Transconductance Amplifiers (OTA) barely get a mention in most university courses

- It is not a standard voltage Op-Amp AND it is a current source  $\bigcirc$

- In many modern PWM ICs however, we will find only a OTA rather than a normal op-amp

- So we may have to design our compensator using an OTA

- But most textbooks and App Notes only deal with normal op-amps

- But a very nice detailed explanation can be found in Christophe Basso's book ISBN 978-1-60807-557-7

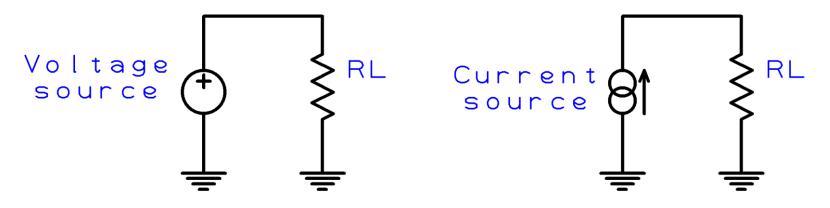

## A Quick Review Voltage and Current Sources

BIRICHA DIGITAL

- An *ideal* voltage source provides whatever current that is necessary to keep the voltage constant across RL as RL changes

- A 1V voltage source with RL = 1 $\Omega$  would source 1A

- The same voltage source with 1M  $\Omega$  would source 1uA

- The same voltage source with  $1\text{m}\Omega$  would source 1000A

- An *ideal* current source provides whatever potential difference that is required to keep the current through RL constant as RL changes

- A 1A current source with RL =  $1\Omega$  would form a p.d. of 1V across RL

- The same current source with 1M  $\Omega$  would form a p.d. of 1MV!

- The same current source with  $1m\Omega$  would form a p.d. of 1mV

#### A Very Quick Review!

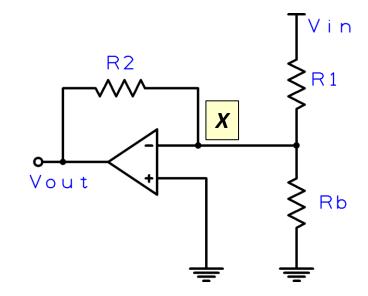

## A Quick Review of Standard Voltage Amplifier

- The standard *ideal* op-amp is effectively a *Controlled Voltage Source*

- Vin is a voltage source and Vout is also a voltage source

BIRICHA DIGITAL

- The current out of the output pin would be whatever is needed to make sure Vout stayed at the desired value  $\rightarrow$  i.e. just like an ideal voltage source

- With an OTA, our output is a current (lout) and not a voltage, so to make a voltage amplifier, we first need to convert the output current to a voltage

- To make an OTA equivalent of a standard op-amp, all we have to do is to connect our feedback impedance to ground instead of point X of the standard op-amp

- Current will now flow out of the lout pin, flow through R2 and a voltage (Vout) will appear across R2

- Output of our OTA, is the potential difference between the non-inverting (Vin+) and the inverting (Vin-) pins of our Op-Amp multiplied by a gain

Vin called "transconductance" or gm

$$Iout = (V_{in+} - V_{in-}).gm$$

- Therefore, gm WILL appear in the transfer function

- But thankfully it is always specified in the datasheet S

Output is a current so we convert to a voltage  $\rightarrow$  Vout = lout x R2

R 1

RFF

Rb

Iout

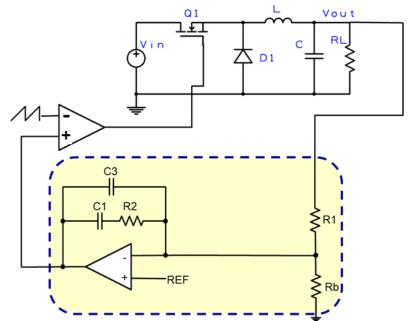

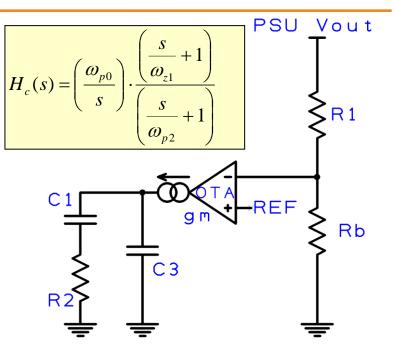

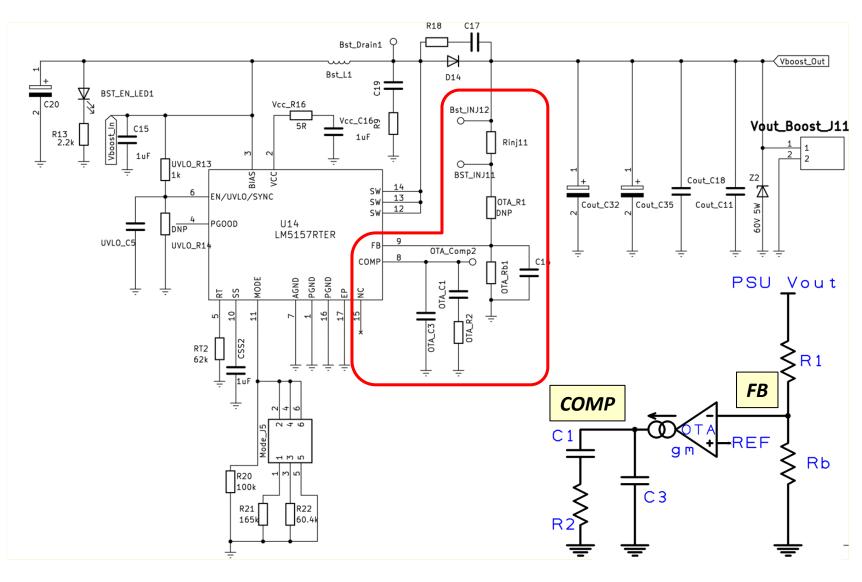

## How to Make a Compensator with an OTA

BIRICHA DIGITAL

- OTA Type II is quite easy, all you have to do is to disconnect the feedback components from point X (of a standard op-amp) and connect to ground

- Current will flow from the OTA output, and the voltage that appears across our impedances will have the frequency response determined by C1, R2, C3 (... and R1 and Rb and gm <sup>(C)</sup>)

- Note that a practical Type III is not simple and therefore it is almost never used\*\*

All we have to do now is to derive the transfer function of our Type II compensator

Luckily this has already been done\* and it is already in Biricha WDS + various other PSU design tools

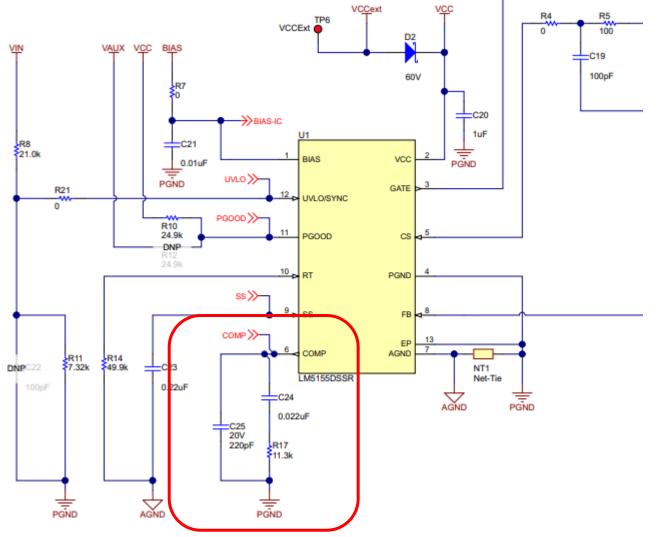

#### LM5155 Boost EVM OTA Example\*

Very easy to say of your chip has an OTA If compensation components are tied to ground then it is an OTA

\* https://www.ti.com/lit/ug/snvu608/snvu608.pdf?ts=1713127283620&ref\_url=https%253A%252F%252Fwww.ti.com%252Ftool%252FLM5155EVM-BST

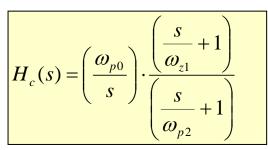

## Type II Compensator with a Standard Voltage Amplifier

• Type II

- 2 poles & 1 zero

- Most commonly used for current mode control (Flybacks/Boost/SEPIC etc.)

- Not suitable for voltage mode Buck or Forward converters (need Type III)

- Transfer function:

- Typically start by positioning our poles and zeros → Day 1 of our workshop or WDS

- Then we select R1 & Rb (more on this later) and then we can calculate everything else

- $\omega$ p0 = frequency of the pole @ origin,  $\omega$ p0 frequency of the 1<sup>st</sup> pole,  $\omega$ z1 = frequency of the 1<sup>st</sup> zero in rad/s for Hz just divide by 2 $\pi$

$$\omega_{z1} = \frac{1}{R_2 C_1}; \omega_{p0} = \frac{1}{R_1 (C_1 + C_3)}; \omega_{p2} = \frac{(C_1 + C_3)}{R_2 C_1 C_3}$$

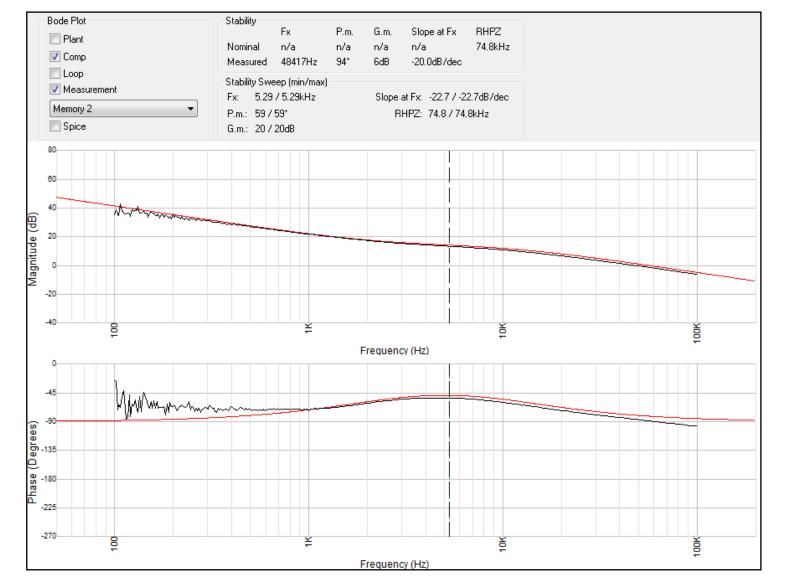

#### Type II Compensator with Standard Voltage Error Amplifier

- Red line: WDS simulation

- Black line: real measurement with Bode100

## Type II Compensator with an OTA

BIRICHA DIGITAL

- Transfer function is exactly the same as the standard op-amp Type II

- But the equations for pole zero placement are different as shown below

- fp0, fp1, fz1 etc. the pole and zero positions in Hz

- First we will use Biricha's WDS Power Supply Design Software to place our poles and zeros

- We cover the principles of how this is done in our workshop

- After selecting the position of our poles and zeros we can select the component values using the following equations\*

- gm is defined in the datasheet and typically displayed in mA/V, uA/V, uSiemens (uS) or in old devices in Mhos

- Typically start by selecting R1 & Rb such that the current through them is >100uA

- Then we can calculate everything else because we have 3 equations & 3 unknowns <sup>(i)</sup>

$$f_{z1} = \frac{1}{2\pi R_2 C_1}; f_{p0} = \frac{g_m R_b}{2\pi (R_1 + R_b) (C_1 + C_3)}; f_{p2} = \frac{(C_1 + C_3)}{2\pi R_2 C_1 C_3}$$

\* All terms denoted by  $\omega$  in the transfer function are in rad/s  $\rightarrow$  for Hz, just divide by  $2\pi$

Design example coming up shortly

- Let us design a CCM Boost with the following specification

- From specifications tab

| Converter Specification     |                  |              |        | Control Parameters |                |                  |   |

|-----------------------------|------------------|--------------|--------|--------------------|----------------|------------------|---|

| Topology: Boo               | ost CCM          |              | $\sim$ | Control Mode:      | Peak Current   | ~                |   |

| Output voltage isolated fro | om primary side: | Non Isolated | ~      |                    | Analog Control | O Digital Contro | k |

| nput Supply:                |                  |              |        | Switching Freque   | ncy            | 350              |   |

| Maximum                     |                  | 5            | v      | Sampling Frequer   | ncy n/a        | n/a 🗸            |   |

| Nominal                     |                  | 5            | v      | Pure Time Delay    |                | n/a              |   |

| Minimum                     |                  | 5            | v      | Crossover Freque   | ency 3.5       | 2 ~              | 1 |

| utput:                      |                  |              | _      | Phase Margin       |                | 75               | 1 |

| Maximum Current             |                  | 1            | Α      |                    |                |                  |   |

| Voltage                     |                  | 9            | V      |                    |                |                  |   |

| Output voltage ripple / overshoot: |                           |        |    |  |  |  |  |  |

|------------------------------------|---------------------------|--------|----|--|--|--|--|--|

| Voltage Ripple (pk-pk)             | 0.5                       | %      |    |  |  |  |  |  |

| Voltage Ripple (pk-pk)             | Voltage Ripple (pk-pk) 45 |        |    |  |  |  |  |  |

| Load Step from 100% to             | 50                        | %      |    |  |  |  |  |  |

| Voltage Overshoot                  | 1800                      | 1800 ~ | mV |  |  |  |  |  |

| Demand Efficiency                  | 85                        | 85 ~   | %  |  |  |  |  |  |

- Under CCM conditions Boost will have a RHPZ issue

- We must use current mode

- In fact under DCM we usually use Imode also mainly so that we can limit the peak of the inductor current

- Under CCM we will have a subharmonic oscillation issue

- We will use a PWM IC with internal slope compensation

- We will use a TI LM5157\*:

- Internal switch

- Internal slope

- Ramp size in datasheet

- Internal current sense circuitry inducing signal amplification

- Current Sense Gain from datasheet

- A Transconductance Amplifier

- VREF and Gm in datasheet

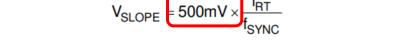

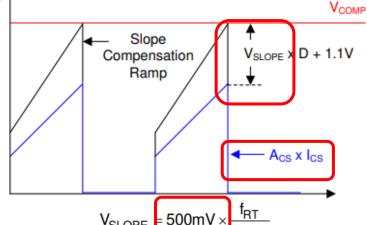

- First we need to extract the data that we/WDS needs from the datasheet\*

- Slope  $\rightarrow$  the chip adds a fixed slope of 500mV without synchronization

0.99

180

2.5

1.01

1.1

2

2.8

1

0.095

V

mA/V

μA

V

v

- Op-Amp Reference Voltage (VREF)

- Current Gain Ri (note: Acs is directly  $\propto$  Ri)

- In WDS Ri is in V/A

- Op-Amp Transconductance (Gm)

- Gm is in uA/V or uSiemens or uMho

Important: make sure the units for Ri and Gm are in the right dimensions Acs is given in V/A as Rsns is internal so this is all we need and Ri = Acs When Rsns is external, Acs it is often given in V/V and we have to multiply by Rsns or Rsns/N

COMP rising (V<sub>UVLO</sub> = 2.0 V)

V<sub>COMP</sub> = 1.2 V

COMP falling

\* https://www.ti.com/product/LM5157

FB reference

Transconductance

COMP sourcing current

COMP clamp voltage

COMP clamp voltage

$\Delta V_{COMP} / \Delta I_{SW}$

BIRICHA DIGITAL

ERROR AMPLIFIER

VREF

Gm

Acs

-  $f_{SYNC}$  is  $f_{RT}$  if clock synchronization is not used

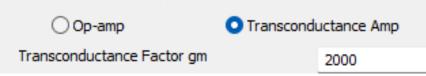

- Gm is given as 2mA/V in the datasheet, but WDS expects it in uA/V

- In Controller Design tab

BIRICHA DIGITAL

• •

- Acs is 0.095V/A from the datasheet in V/A, therefore Ri = Acs = 0.095 V/A

- In Controller Design Tab

| Current Sense and Slope Compensation |                           |     |        |          |  |  |  |

|--------------------------------------|---------------------------|-----|--------|----------|--|--|--|

| Current Sense Gain <                 | Current Sense Gain < 0.34 |     |        |          |  |  |  |

| Magnetizing "Free" Ramp              | 0                         |     |        | V(pk-pk) |  |  |  |

| Optimal External Ramp                | 0.08                      |     |        | V(pk-pk) |  |  |  |

| Amount of Ramp to Add                | 0.08                      | 0.5 | $\sim$ | V(pk-pk) |  |  |  |

| Ramp Slope                           | 175                       |     |        | mV/usec  |  |  |  |

| V. on Current Sense Pin              | 0.78                      |     |        | V        |  |  |  |

- From the datasheet we know that our OTA's VREF = 1V

- In Analog (Non-Isolated tab)

| Error Amplifier   |       |

|-------------------|-------|

| Reference Voltage | 1 ~ V |

|                   |       |

Please note that:

uMho/µS

- Acs is already in V/A as in LM5157, our current sense resistor Rsns is internal

- If Rsns is external (e.g. TPS40210) then Acs is often given as the gain of the internal current sense amplifier in V/V or with no units

- Then we must multiply by Acs by external Rsns or Rsns/N → more on this later

- A/V, Siemens (S) and Mho are all the same units

#### CCM Boost Converter Control Loop Real Design Exampleoler Poles and Zeros

- WDS can now calculate our poles and zeros (on the right)

- In Analog (Controller Design tab)

BIRICHA DIGITAL

- Or you can place them yourselves by hand or with other tools

- You or WDS can now calculate our Rs and Cs based on

$$f_{z1} = \frac{1}{2\pi R_2 C_1} ; f_{p0} = \frac{g_m R_b}{2\pi (R_1 + R_b) (C_1 + C_3)} ; f_{p2} = \frac{(C_1 + C_3)}{2\pi R_2 C_1 C_3}$$

- Typically we specify how much current we wish to flow down R1 & Rb and then everything else is worked out by WDS

- Try to keep the current >100uA for better radiated immunity in the EMC test chamber

|                |                   |       |     |   |    | Control | ler |

|----------------|-------------------|-------|-----|---|----|---------|-----|

| Sampling Divid | er                |       |     |   |    | R2      |     |

| Desired cur    | rrent through div | /ider | 0.5 | ~ | mA | R3      |     |

| R1             |                   | 16    | 16  | ~ | kΩ | C1      |     |

| Rb             |                   | 2     | ]   |   | kΩ | C2      |     |

| Actual curr    | ent through pd    | 0.5   | ]   |   | mA | C3      |     |

|                |                   |       |     |   |    |         |     |

| 4.35  | 4.32                        | ~                                         | kΩ                                                                      |

|-------|-----------------------------|-------------------------------------------|-------------------------------------------------------------------------|

| n/a   | n/a                         | ~                                         | kΩ                                                                      |

| 83.93 | 100                         | ~                                         | nF                                                                      |

| n/a   | n/a                         | ~                                         | nF                                                                      |

| 1.76  | 2.2                         | ~                                         | nF                                                                      |

|       | 4.35<br>n/a<br>83.93<br>n/a | 4.35 4.32   n/a n/a   83.93 100   n/a n/a | 4.35   4.32   ~     n/a   n/a   ~     83.93   100   ~     n/a   n/a   ~ |

| IE                 |              |                 |

|--------------------|--------------|-----------------|

| 🗿 Automatic        | placement OM | anual placement |

| Pole at the origin | 412.78       | 412.78 V Hz     |

| First Pole         | 21277.4      | 21277.4 V Hz    |

| Second Pole        | n/a          | n/a 🗸 Hz        |

| First Zero         | 435.86       | 435.86 🗸 Hz     |

| Second Zero        | n/a          | n/a 🗸 Hz        |

|                    |              |                 |

#### Our Design is Complete! 🙂

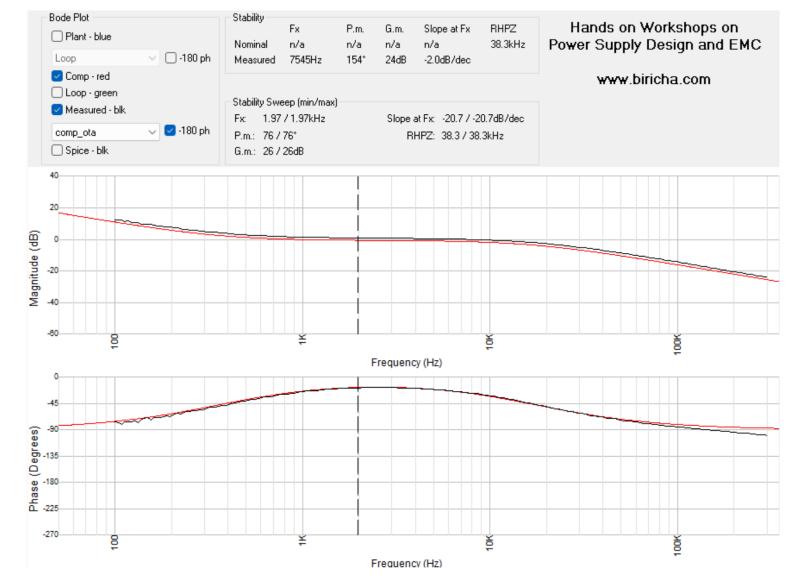

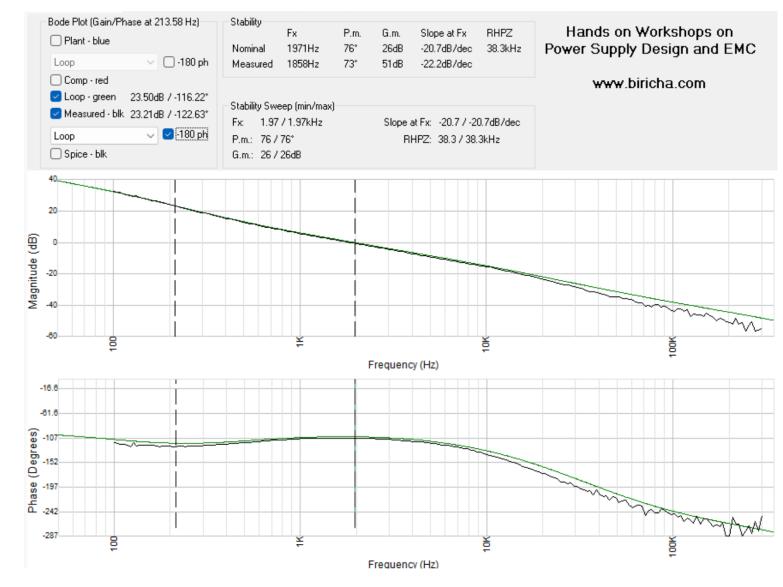

#### **OTA Based Boost Compensator Measurement**

- Red line: WDS simulation

- Black line: real measurement with Bode100

Imode: 4 - 19 © S. A. Shirsavar - Biricha Digital Power Ltd 2024

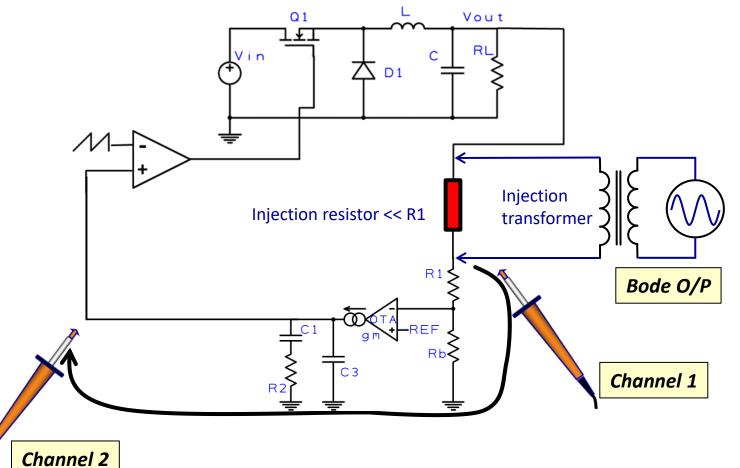

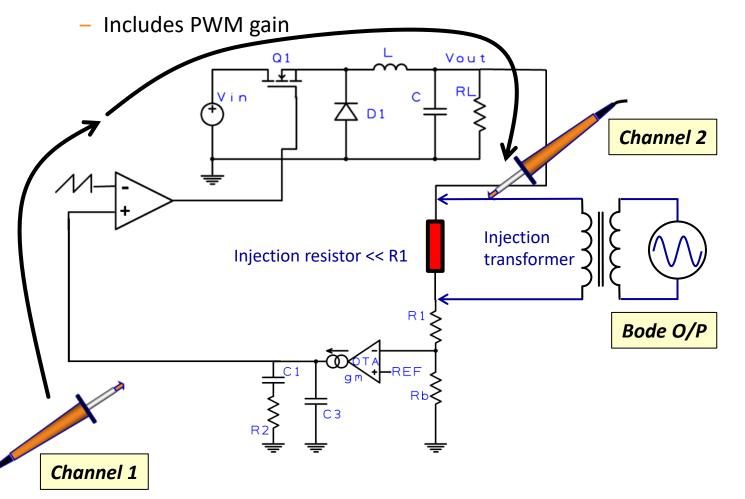

Measuring the compensator's response

BIRICHA DIGITAL

- Measures the frequency response of the compensator

• Measure the plant's response:

BIRICHA DIGITAL

- Also known as the control to output transfer function

Imode: 4 - 21 © S. A. Shirsavar - Biricha Digital Power Ltd 2024

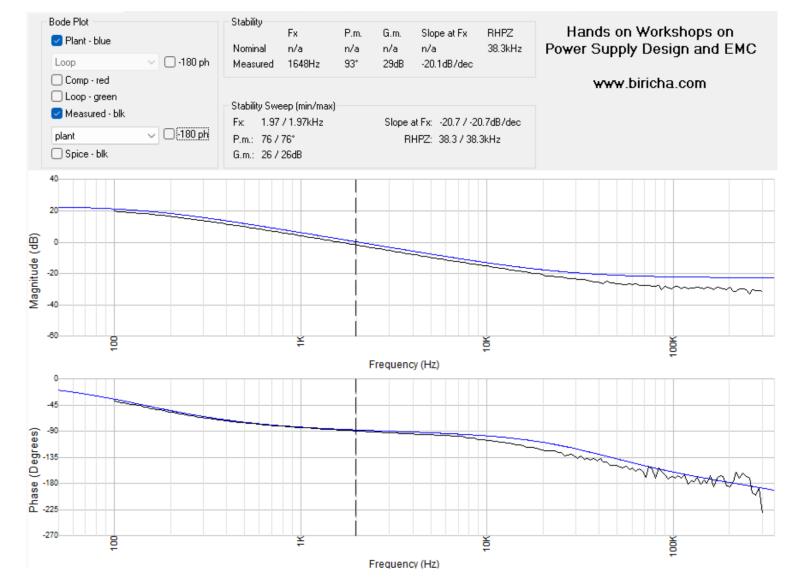

#### OTA Based Boost Boost's Plant Measurement

- Blue line: WDS simulation

- Black line: real measurement with Bode100

Imode: 4 - 22 © S. A. Shirsavar - Biricha Digital Power Ltd 2024

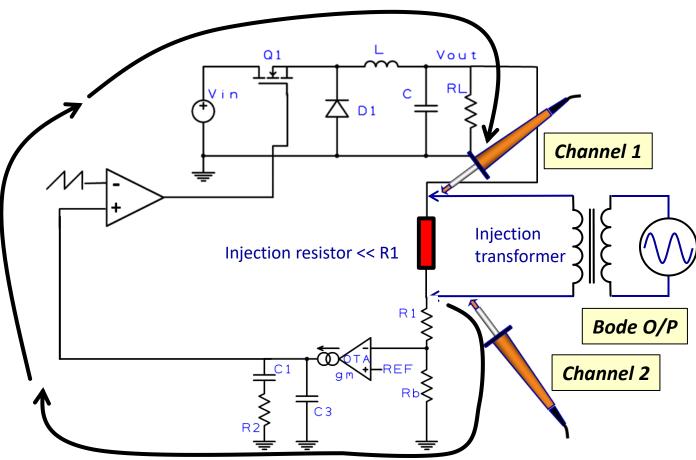

## **OTA Based Boost Loop Measurement**

Measuring the loop response

BIRICHA DIGITAL

Measures the frequency response of the compensator, PWM and plant combined

#### **OTA Based Boost Loop Measurement**

- Green line: WDS simulation

- Black line: real measurement with Bode100

Imode: 4 - 24 © S. A. Shirsavar - Biricha Digital Power Ltd 2024

## OTA Based Boost Step Load (50% $\rightarrow$ 100%)

| 쒏 Utility                                                                              | 🖵 Display         | र्गी Acquire                       | 🏲 Trigger               | # Cursors                    | 📐 Measure  | 🕅 Math | ই Analysis              | SIGLENT Ready<br>f(C1) < 2.0Hz | 🗐 cu      | RSORS                                                                                                                                        |

|----------------------------------------------------------------------------------------|-------------------|------------------------------------|-------------------------|------------------------------|------------|--------|-------------------------|--------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------|

| ΔX= 995u<br>1/ΔX= 1.005<br>X2= 1.005<br>X1= 10us<br>ΔY= 0.0V<br>Y2= 200.0<br>Y1= 200.0 | 05kHz<br>ms<br>mV |                                    |                         | hallafi harigani 1916-ya<br> |            |        |                         |                                |           | Y2                                                                                                                                           |

| en sitt sitt sitt sitt sitt sitt sitt sit                                              |                   |                                    |                         |                              |            |        |                         |                                |           | nten 1990 tit tit ten ten<br>Anders der seken sin der se |

|                                                                                        |                   |                                    |                         |                              |            |        |                         |                                |           |                                                                                                                                              |

|                                                                                        |                   |                                    |                         |                              |            |        |                         |                                |           | · · · · ·                                                                                                                                    |

| MEASURE                                                                                |                   | Mean(C1)                           | - To                    | р(C1)                        | X1<br>Freq | (C1)   | X2<br>Mean(C2)          | :<br>— Top(C                   | 4)        | - X                                                                                                                                          |

| Value                                                                                  |                   | >4.5793492V( 1                     |                         | 0417V( ↑ )                   | ***        |        | 10.324696n              |                                |           |                                                                                                                                              |

| C1 DC1<br>10X 2.00<br>FULL 0.0                                                         | W/ 10X 50.0       | xC1M C4<br>)mV/ 1V/A<br>0.00V FULL | DC1M<br>2.00A/<br>0.00A | <u> </u>                     |            |        | Timeb<br>397ns<br>1.00M |                                | nal 7.90V | 뮮<br>00:08:59<br>2024/3/30                                                                                                                   |

## Biricha Workshops

BIRICHA DIGITAL

- June 2024 Freiham Germany

- Analog PSU Design

- Digital PSU Design

- EMC Filter Design

- New online workshops Q4 2024

- Register here to receive updates + free WDS:

- www.biricha.com/omicron.html

#### Upcoming Workshops

Digital Power Supply and PFC Design Workshop with STM32 April 23rd - 26th 2024 Austin, TX USA

#### SOLD OUT

Analog Power Supply and PFC Design Workshop with TI June 4th - 7th 2024 Freiham, Munich Germany

REGISTER

Digital Power Supply and PFC Design Workshop with dsPIC33C June 4th - 7th 2024 Freiham, Munich Germany

REGISTER

EMC Input Filter Design Workshop June 10th - 12th 2024 Freiham, Munich Germany

REGISTER